## **Declaration of Authorship**

I, Antony Johan Karels, hereby declare that I am the sole author of the work entitled:

"From Concept to Console: FortressFlash, a Secure Field Deployment Tool for FortiGate and Beyond"

here enclosed, and that I have compiled it in my own words, that I have not used any other than the cited sources and aids, and that all parts of this work, which I have adopted from other sources, are acknowledged and designated as such. I also confirm that this work has not been submitted previously or elsewhere.

Signed in Stillwater, Minnesota, United States, on 25 August 2025.

ntony John

**Antony Johan Karels**

#### **Integrity Note:**

For verification purposes, the SHA-256 hash of the officially submitted PDF is archived at:

### University of Luxembourg

FACULTY OF SCIENCE, TECHNOLOGY AND MEDICINE

ERASMUS MUNDUS JOINT MASTER IN CYBERSECURITY (CYBERUS)

### **Master's Thesis**

## From Concept to Console: FortressFlash, A Secure Field Deployment Tool for FortiGate and Beyond

Author: Antony Johan Karels

STUDENT No: 0232759843

PROGRAM SUPERVISOR: Assoc. Prof. Tegawendé Bissyandé

ACADEMIC SUPERVISOR: Assoc. Prof. Christian Fisch

Submitted: 25 August 2025

Pages: 74 Words: 20,579 Characters: 139,848

## Acknowledgements

This thesis marks the culmination of my journey through the CYBERUS Erasmus Mundus Joint Master's Degree program, and I am deeply grateful to those who supported me along the way.

To my fellow **2023-2025 CYBERUS** cohort — thank you for the shared experiences, encouragement, and solidarity throughout this international academic adventure. From Lorient to Tallinn to Luxembourg and beyond, your presence made the challenges lighter and the memories brighter

I extend my sincere thanks to **Professor Guy Gogniat** of the University of Southern Brittany for his support during the first year of the program, and to **Associate Professor Tegawendé F. Bissyandé** at the University of Luxembourg for his flexibility and trust in allowing me to pursue this thesis independently. I am also grateful to my academic supervisor, **Associate Professor Christian Fisch**, for his guidance and encouragement throughout this project.

The initial spark for this project came from hands-on experience in a previous workplace, where I was fortunate to have colleagues who supported early exploration. In particular, I would like to thank **Beth Taylor**, whose encouragement to pursue the CYBERUS program gave me the confidence to take that opportunity despite the uncertainty of a new position. In the months that followed, she continued to support the idea of this project by helping to procure initial hardware and allowing time for some of the early development work, contributions that ultimately shaped the direction of this thesis.

I also wish to acknowledge the use of OpenAI's ChatGPT as a writing and brainstorming companion during many solitary sessions. Its assistance in refining drafts, exploring phrasing, and maintaining momentum was a valuable aid in bringing this work to completion.

The direction, design, and execution of this project have been entirely my own, yet they were built on a foundation shaped by many others. I am thankful for every challenge that helped forge this outcome, for every opportunity that made it possible, and for the set-apart grace that carried me through to its completion. To all who offered guidance, support, or simply a word of encouragement along the way: **Thank You.**

## **Abstract**

Managed-service providers often ask Level-1 technicians to stage FortiGate firewalls under tight change windows. In practice, first-boot turn-up is slowed by repeated laptop tethering, reconfiguring the admin PC onto the factory management subnet, and other setup friction before a vetted baseline can be applied. FortressFlash addresses this usability gap with a self-contained, Raspberry Pi Pico–based appliance that lets L1 staff deliver a *pre-vetted*, *version-controlled* baseline configuration over UART—without a laptop—while embedding hardware-rooted security. The current prototype couples a Waveshare RP2040-Plus, capacitive-touch display, and microSD storage with modular MicroPython firmware. Security primitives—planned for migration to Raspberry Pi Pico 2 W—include signed/attested boot, OTP-sealed keys, and SHA-256 integrity checks.

A pragmatic three-phase methodology guided development: rapid hardware familiarization, iterative firmware prototyping, and STRIDE-aligned threat modeling. Bench trials on FortiGate 60E units validate stable console-session establishment (20/20 successful logins without resets), authenticated CLI interaction, SD-backed profile selection, and live scroll logging. At submission time, integration of the end-to-end *automated* first-boot push is not yet complete; the evaluation therefore reports component-level behavior and documents the dispatcher design intended to enable fast, repeatable deployment once integrated.

Threat analysis motivates PIN-gated access, file-level encryption of removable media, console-only service accounts, and optional device—firewall binding to mitigate spoofing, tampering, and credential-exposure risks. A near-term roadmap details configuration signing, attested boot/firmware, and role-based access. Beyond its academic contribution, FortressFlash's portable, zero-laptop workflow and planned cryptographic safeguards are designed with regulatory frameworks such as NIST 800-171/CMMC in mind. The underlying architecture remains vendor-agnostic, and its UART-driven approach can be extended to other CLI-centric platforms that share similar staging challenges.

In sum, this thesis documents the design, partial implementation, and security analysis of a field-oriented tool intended to turn error-prone, laptop-dependent staging into a repeatable, auditable process—while charting a clear path to multi-vendor expansion.

**Keywords:** Fortinet, FortiGate, firewall configuration, CLI automation, Raspberry Pi Pico, UART, MicroPython, STRIDE threat modeling, secure boot, CMMC, embedded systems security, managed service providers (MSP)

## **Contents**

| A  | cknow   | riedgements                                          | 1   |

|----|---------|------------------------------------------------------|-----|

| Al | ostrac  | et .                                                 | ii  |

| Li | st of l | Figures                                              | v   |

| Li | st of T | Tables                                               | vii |

| 1  | Intr    | oduction                                             | 1   |

|    | 1.1     | Background and Motivation                            | 1   |

|    | 1.2     | Problem Statement                                    | 6   |

|    | 1.3     | Objectives and Scope                                 | 7   |

|    | 1.4     | Methodological Approach                              | 8   |

| 2  | Har     | dware Design                                         | 11  |

|    | 2.1     | Goals and Constraints                                | 11  |

|    | 2.2     | Candidate MCU Platforms and Selection                | 13  |

|    | 2.3     | Subsystems: Display, Touchscreen, Storage, and Power | 17  |

|    | 2.4     | Subsystems: Serial UART                              | 19  |

|    | 2.5     | Enclosure and Connector Integration                  | 22  |

|    | 2.6     | Complete FortressFlash Assembly                      | 23  |

| 3  | Soft    | ware Design                                          | 25  |

|    | 3.1     | MicroPython for Rapid Prototyping                    | 25  |

|    | 3.2     | Firmware Architecture and Operational Flow           | 25  |

|    | 3.3     | Touchscreen UI and User Flow                         | 29  |

|    | 3.4     | SD Card Configuration Management                     | 32  |

|    | 3.5     | Firmware Architecture and Developer Workflow         | 32  |

| 4  | Thr     | eat Modeling                                         | 35  |

|    | 4.1     | Overview                                             | 35  |

|    | 4 2     | What Are We Working On?                              | 35  |

|    | 4.3   | What Can Go Wrong?                      | 36 |

|----|-------|-----------------------------------------|----|

|    | 4.4   | What Are We Going To Do About It?       | 38 |

|    | 4.5   | Did We Do A Good Enough Job?            | 40 |

| 5  | Eval  | uation and Use Cases                    | 42 |

|    | 5.1   | Evaluation Setup                        | 42 |

|    | 5.2   | Preliminary Observations and Results    | 44 |

|    | 5.3   | Deployment Scenario                     | 46 |

| 6  | Prot  | otype to Product                        | 48 |

|    | 6.1   | Brand Identity and Positioning          | 48 |

|    | 6.2   | Business Model Canvas                   | 49 |

|    | 6.3   | SWOT Analysis                           | 51 |

|    | 6.4   | Go-To-Market Strategy                   | 52 |

|    | 6.5   | Pricing and monetization                | 52 |

|    | 6.6   | Strategic Insights                      | 54 |

| 7  | Futu  | re Work                                 | 55 |

|    | 7.1   | Expansion to Other Vendors or Platforms | 55 |

|    | 7.2   | Out-of-Band Management Gateway          | 56 |

|    | 7.3   | Short-Range Wireless: BLE & Wi-Fi       | 57 |

|    | 7.4   | Long-Range Wireless: LoRa               | 58 |

|    | 7.5   | API Mode over TCP/IP                    | 61 |

|    | 7.6   | Intent-Based Networking                 | 62 |

| 8  | Con   | clusion                                 | 64 |

| Aŗ | pend  | ix A: Supplementary Materials           | 66 |

|    | A.1   | Bill of Materials and Equipment         | 66 |

|    | A.2   | Pinout Diagrams                         | 67 |

|    | A.3   | 3D Model Reference                      | 68 |

|    | A.4   | Benchmarks                              | 69 |

|    | A.5   | User Experience and Interface           | 70 |

|    | A.6   | Brand Assets                            | 73 |

|    | A.7   | Additional Images                       | 74 |

| Re | feren | ces                                     | 75 |

# **List of Figures**

| 1.1 | FortiLab — three stacked FortiGate frewans and a Netgear GS/241P switch                   | 2  |

|-----|-------------------------------------------------------------------------------------------|----|

| 1.2 | ICS/OT pentesting lab setup, featuring a Raspberry Pi 2 B+                                | 3  |

| 1.3 | Early prototyping chaos: various MCUs and serial experiments in progress                  | 5  |

| 2.1 | FortressFlash hardware block diagram                                                      | 13 |

| 2.2 | Time-based MicroPython benchmarks on MCU-class boards                                     | 17 |

| 2.3 | $Wave share\ RP2040-Plus\ microcontroller\ and\ Pico-Res Touch-LCD-2.8\ touch screen.\ .$ | 18 |

| 2.4 | Signal flow from FortiGate RJ-45 console port to UART0 on the MCU                         | 20 |

| 2.5 | Generic RS-232↔TTL adapter causing thermal faults                                         | 22 |

| 2.6 | Waveshare 2.8" LCD and RP2040-Plus mounted in 3d-printed ABS case                         | 23 |

| 2.7 | Complete FortressFlash assembly                                                           | 24 |

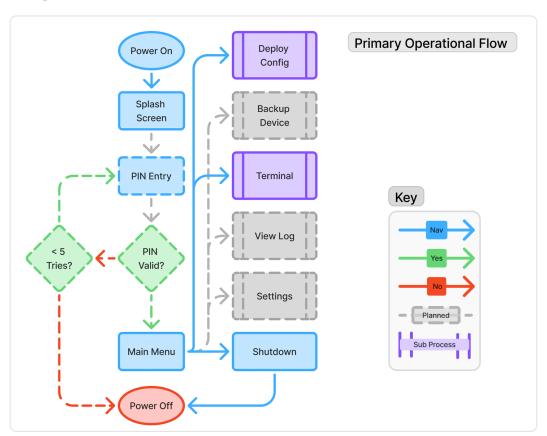

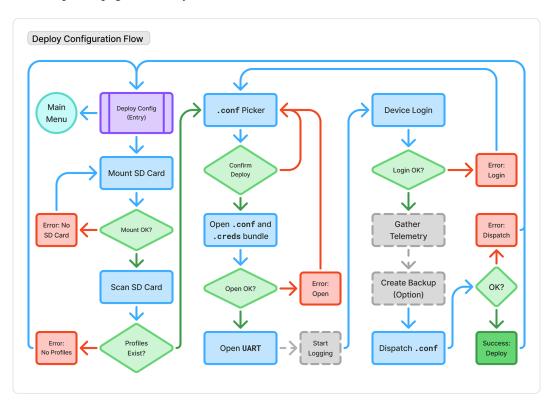

| 3.1 | Primary operational flow                                                                  | 29 |

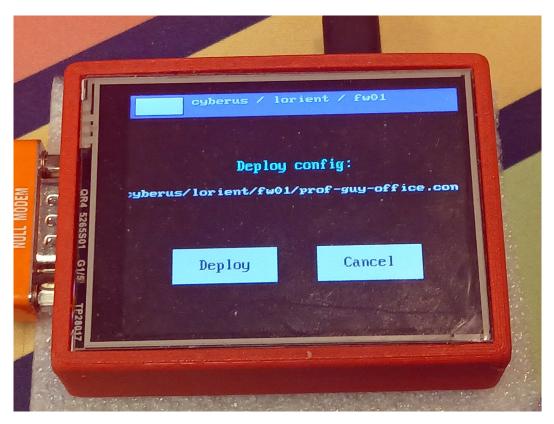

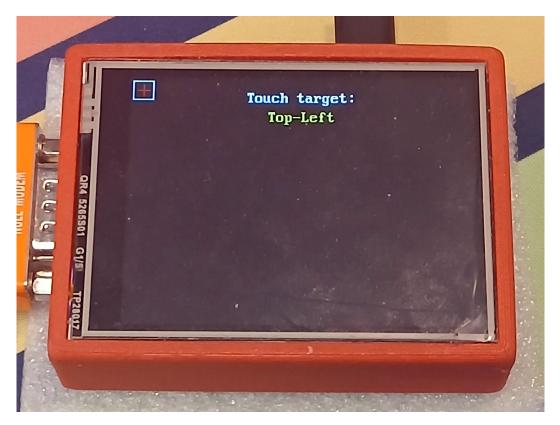

| 3.2 | Deploy Config subprocess                                                                  | 30 |

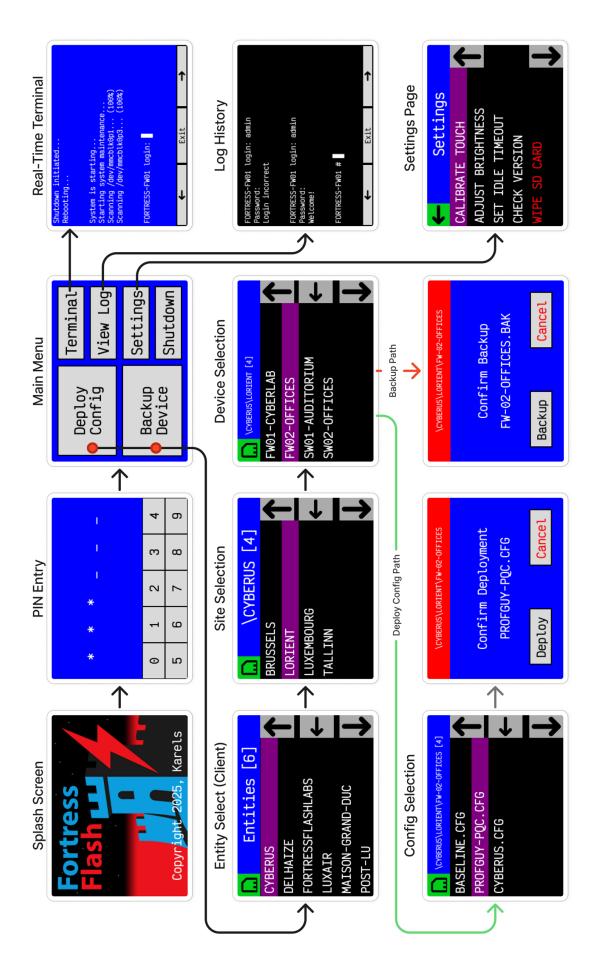

| 3.3 | FortressFlash UX flow: primary screens, navigation paths, and core functions              | 31 |

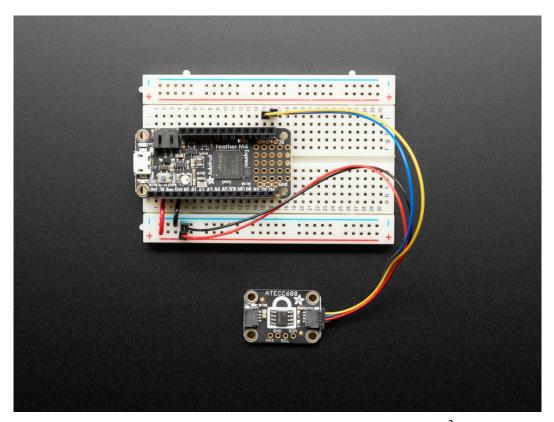

| 4.1 | Adafruit ATECC608A secure element breakout board connected via $I^2C$                     | 39 |

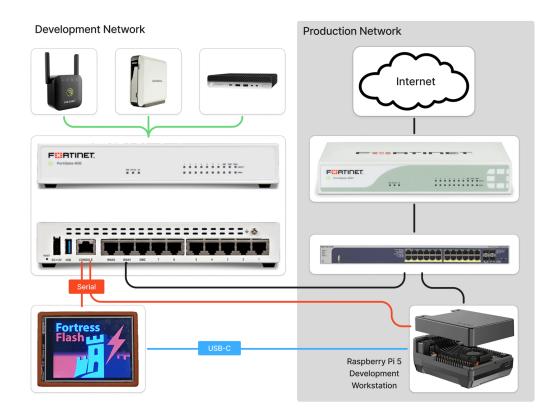

| 5.1 | Evaluation bench topology                                                                 | 43 |

| 5.2 | Successful FortiGate login via FortressFlash REPL and verified console prompt             | 45 |

| 6.1 | FortressFlash brand identity mark                                                         | 49 |

| 6.2 | FortressFlash Business Model Canvas                                                       | 50 |

| 7.1 | FortressFlash connected to a Palo Alto PA-200 firewall                                    | 56 |

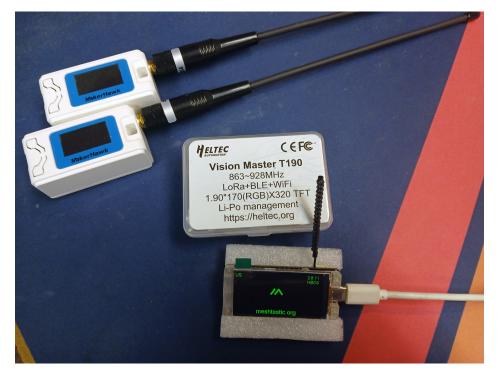

| 7.2 | Various LoRa MCUs: Heltec WiFi LoRa 32 V3 and Vison Master T190                           | 59 |

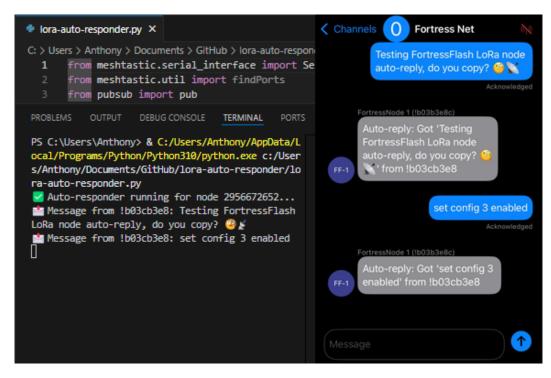

| 7.3 | LoRa auto-responder test in action                                                        | 60 |

| 7.4 | LoRa auto-reply range test (Google Maps): 315m (1,035ft)                                  | 61 |

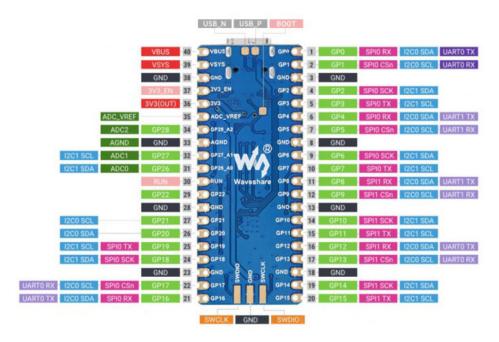

| A.1 | Waveshare RP2040-Plus pinout diagram                                                      | 67 |

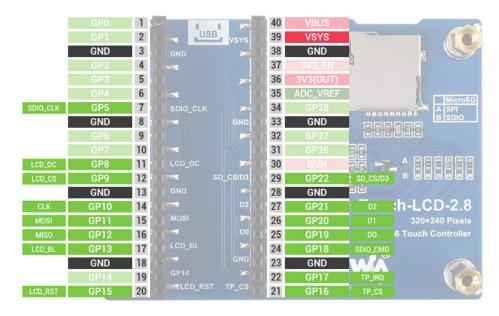

| A.2 | Waveshare ResTouch 2.8" LCD pinout diagram                                                | 67 |

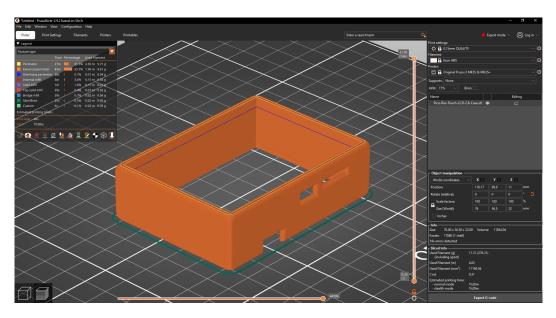

| A.3 | Original STL model by Tasuku Suzuki.                                                      | 68 |

| A.4 | Enclosure being printed on a Prusa i3 MK3S+ using eSUN red ABS filament                   | 68 |

| A.5  | Benchmark results (MOPS) comparing Pico and Pico 2 at native clock speeds | 69 |

|------|---------------------------------------------------------------------------|----|

| A.6  | Benchmark results (MOPS) comparing Pico and Pico 2 normalized to 100 MHz  | 69 |

| A.7  | FortressFlash status and error screens                                    | 70 |

| A.8  | FortressFlash main menu interface                                         | 70 |

| A.9  | Profile selection and deployment workflow on FortressFlash                | 71 |

| A.10 | Touchscreen calibration utility on FortressFlash                          | 72 |

| A.11 | Branded FortressFlash apparel                                             | 73 |

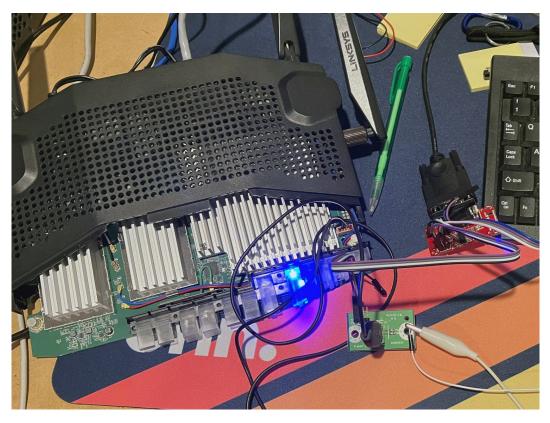

| A.12 | Recovering a Linksys WRT32X using its internal serial header              | 74 |

## **List of Tables**

| 1.1 | Project phases and current status                         | 10 |

|-----|-----------------------------------------------------------|----|

| 2.1 | Comparison of candidate boards by specification           | 15 |

| 2.2 | MicroPython Benchmark Results Across Selected Platforms   | 16 |

| 2.3 | Prototype GPIO and Peripheral-Bus Assignments             | 19 |

| 3.1 | Firmware feature inventory and implementation status      | 26 |

| 6.1 | SWOT analysis for the FortressFlash concept               | 51 |

| 6.2 | Stage-gated pricing framework for FortressFlash           | 53 |

| 6.3 | Optional and future upsell levers                         | 53 |

| A.1 | Bill of Materials for FortressFlash Prototype             | 66 |

| A.2 | Components Evaluated but Not Incorporated in Final Design | 66 |

| A 3 | Lab and Test Environment Hardware                         | 66 |

## **Chapter 1: Introduction**

#### 1.1 Background and Motivation

Initial Experience in FortiGate Deployment. I was first introduced to the FortiGate platform in spring 2023 while working as a project engineer for a managed service provider (MSP) in Minnesota that offered IT support and cybersecurity services to small and medium-sized enterprises (SMEs). As a Fortinet partner, the company standardized on FortiGate appliances across all client networks. My role involved deploying new devices during customer onboarding by following internal documentation to apply a base configuration and adapt it to each client's network. After gaining confidence with features like intrusion detection (IDS), DNS filtering, and SSL VPNs, I was assigned a more advanced setup: configuring SSL VPN access via FortiClient with Azure Entra ID authentication and multi-factor login using Microsoft Authenticator.

Most configurations were handled through the GUI, but key steps in Microsoft and Fortinet documentation often required command-line interface (CLI) commands—some buried deep in the interface, others unavailable outside the terminal. With so many features and options, the CLI often proved faster and more precise, especially for tasks like setting SAML URLs and group mappings. While I initially preferred the GUI as I learned the platform, I quickly saw that mastering the CLI would boost both efficiency and understanding. That became clear when I learned how to transfer configs between devices by copying CLI blocks from one file into another and loading them directly.

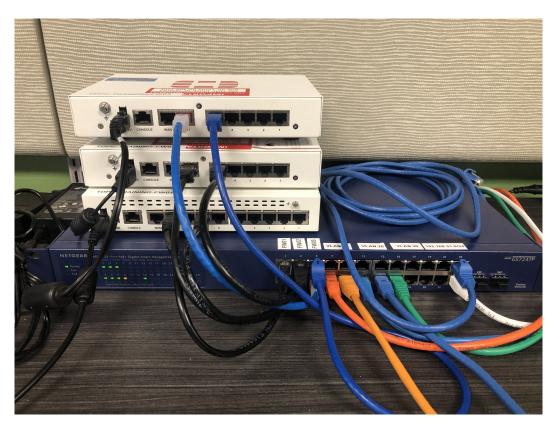

**FortiLab and Multi-VLAN Testing.** To sharpen my FortiGate skills—and give our help-desk a safe playground—I scavenged a decommissioned Netgear GS724TP switch and three spare FortiGate appliances to build "FortiLab" (Figure 1.1). Each firewall sat on its own tagged VLAN, with WAN links back to the office network, letting us flash different firmware versions and hardware models in complete isolation.<sup>1</sup>

The lab's sandboxed topology meant we could rehearse upgrade paths and experiment with policy sets without risking production. Documenting the wiring, VLAN plan, and backup configurations in the company's configuration management database (CMDB)—and labeling every port—sharpened my network-design discipline and left a reusable test bed the team still relies on today.

<sup>&</sup>lt;sup>1</sup>Admittedly, the VLANs weren't strictly necessary—each FortiGate had spare ports. But the extra complexity made things more interesting, and gave me an excuse to laminate a port mapping table.

Figure 1.1: "FortiLab" — three stacked FortiGate firewalls linked to a Netgear GS724TP switch, each on its own VLAN for safe experimentation.

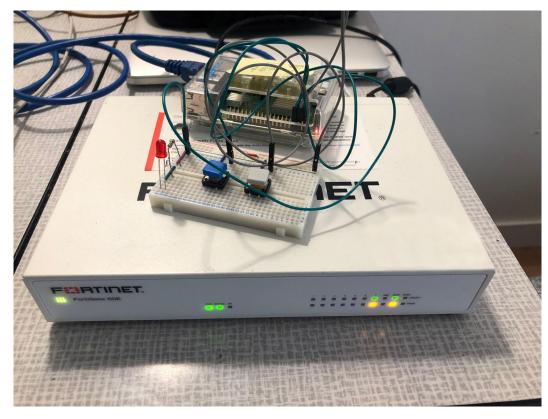

**ICS Pentesting Lab.** During the second semester of the Cyberus program, while studying in Lorient, France, I participated in a group project focused on industrial control system (ICS) security. Our task was to demonstrate practical pentesting techniques within a simulated operational technology (OT) environment. I led the lab design and implementation as part of a group assignment, documented in our internal ICS/OT pentesting report.<sup>2</sup> Naturally, I incorporated the FortiGate firewall that my employer had provided for hands-on practice.

The lab environment combined a Raspberry Pi 2 B+ running OpenPLC, a breadboard circuit simulating digital I/O, and the FortiGate 60E acting as a network gateway and security perimeter. The OpenPLC was programmed with ladder logic to control LEDs and receive inputs from physical buttons, mimicking basic industrial processes. This hands-on project deepened my understanding of microcontroller integration in OT networks and re-ignited my interest in small-form-factor hardware (Figure 1.2).

**Deploying FortiGate in FIPS-CC Mode.** Following the ICS/OT pentesting experience, I returned to Minnesota for a summer internship that focused on helping a client prepare for the Level 2 Cybersecurity Maturity Model Certification (CMMC). Although the project primarily addressed

<sup>&</sup>lt;sup>2</sup>Available at https://cyberus.lu/reports/Karels\_ICS-Pentest\_Cyberus\_2024.pdf. See also [1].

Figure 1.2: ICS/OT pentesting lab setup, featuring a Raspberry Pi 2 B+ running OpenPLC, breadboard with I/O circuit, and a FortiGate firewall for segmentation and perimeter security.

broader compliance topics, my final assignment required directly working with FortiGate firewalls in a CLI-only environment. The task involved cloning a configuration from a standard device onto a new unit running the FIPS-CC validated firmware, which enforces command-line usage by design and disables the graphical interface during writing of the new firmware.

This hands-on experience not only deepened my understanding of FortiGate's CLI structure and constraints, but also highlighted the operational challenges faced by small teams when deploying secure configurations under regulatory frameworks like CMMC. The concept for a portable CLI automation device began to take shape during this phase, inspired by the desire to streamline such deployments in resource-constrained environments.

During this period I also completed both the Fortinet Certified Fundamentals (FCF) and Fortinet Certified Associate (FCA) certifications, which cover core principles of network security and foundational skills for configuring and managing FortiGate devices.<sup>3</sup> A copy of the earned certificates, along with configuration tasks, the original proposal, and additional project notes, are included in the final internship report.<sup>4</sup>

<sup>&</sup>lt;sup>3</sup>Completing both certifications qualified me to receive a FortiGate 70F appliance bundled with a one-year subscription to Fortinet's security services (e.g., FortiGuard updates, support, and licensing) through their promotional program — a generous offer that, despite my enthusiastic compliance, mysteriously never materialized.

<sup>&</sup>lt;sup>4</sup>Available at https://cyberus.lu/reports/Karels\_CMMC-Internship\_Cyberus\_2024.pdf. See also [2].

Automating FortiGate Setup over Serial. While working on CMMC-related tasks during my internship, I simultaneously began experimenting with serial communication to the FortiGate using a USB console cable. What began as a simple Python script—logging into the CLI, issuing basic commands, and printing the output—quickly evolved into more advanced automation. I developed additional scripts to enable or disable GUI access via HTTPS on the WAN port and to modify LAN/WAN IP settings. These small utilities made initial configuration easier by avoiding the need to manually reconfigure a workstation's NIC to match the firewall's default IP range.

As noted earlier, deploying new FortiGate devices involved following a standardized base configuration. While this responsibility usually fell to Project Technicians, there were frequent situations where Helpdesk staff could have benefited from the ability to perform the task themselves. Unfortunately, due to limited experience with the devices, this responsibility was rarely delegated—despite the organization's need to more efficiently distribute onboarding tasks.

With this challenge in mind, I aimed to leverage the serial connection to automate deployment of the base configuration using Python. The idea was simple: Helpdesk staff could unbox a new device, plug in the console cable, run a script, and have the base configuration applied automatically. Any unique values—such as licensing credentials or client-specific settings—could then be verified and adjusted via the GUI. I also introduced interactive prompts to collect dynamic values like the hostname and IP addresses, with the goal of gradually expanding this capability to support more flexible and parameterized deployments.

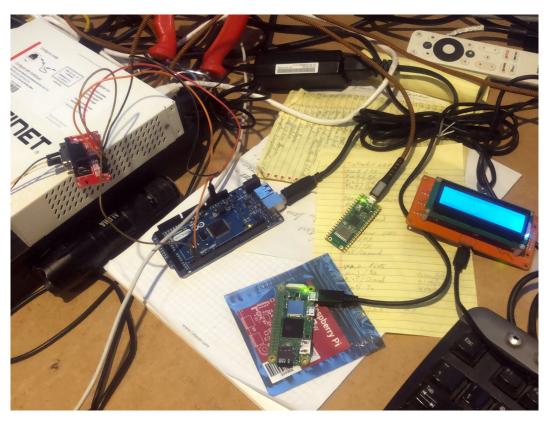

**Exploring MCU Options for Serial Control.** Following my experiments using Python to interface with the FortiGate over a console cable—and still inspired by the ICS OpenPLC demonstration—I began exploring a variety of microcontroller unit (MCU) platforms. Initially revisiting the ICS lab, I rebuilt the breadboard created in the University's lab using personally owned components. I then transitioned to a TinkerKit LCD unit based on the Arduino Leonardo, with the basic goal of refamiliarizing myself with the hardware and the Arduino C environment. Early experiments included output to LCD screens, reading sensor data, button input, and controlling LEDs. These quickly evolved to include Ethernet shields and the development of simple web servers capable of reading and writing data over TCP/IP to interact with connected peripherals.<sup>5</sup>

Building on my initial success communicating with the FortiGate using Python and a console cable, I wanted to explore whether similar functionality could be achieved using a microcontroller. With several platforms already in possession—and an eagerness to expand my options—I acquired additional development boards to evaluate their suitability for the task (Figure 1.3; see also Section 2.2,

<sup>&</sup>lt;sup>5</sup>Examples included reading temperature sensors, toggling LEDs, and triggering a PowerShell script (source code at https://github.com/aku762/listenlock) to remotely lock my workstation via a network-connected button.

Candidate MCU Platforms and Selection for a detailed comparison).<sup>6</sup>

The result of this exploration culminates in this project's deliverable: a purpose-built prototype initially nicknamed the *FortiProgrammer*<sup>7</sup> during early testing, but ultimately branded as **Fortress-Flash** to establish its product identity. The device is introduced briefly below and described in full detail in Chapter 2, Hardware Design.

Figure 1.3: Early prototyping chaos: various MCUs and serial experiments in progress. From left to right: Arduino Mega, Raspberry Pi 2 B+, Raspberry Pi Pico W, and a TinkerKit LCD module based on the Arduino Leonardo architecture.

Entrepreneurial Case Study Influence. During the third semester of the Cyberus program, while attending in-person courses in Luxembourg, our cohort participated in an entrepreneurship course taught by Prof. Christian Fisch. One of the assigned case studies<sup>8</sup> focused on Fortinet and its co-founder and CEO, Ken Xie [3]. The study explored Xie's decision to resist market pressure from analysts encouraging a shift toward cloud-first messaging and splashy marketing. Instead, he remained committed to a hardware-centric strategy, emphasizing Fortinet's long-term investment in ASIC development and product integration. The hardware-first strategy described in the case

<sup>&</sup>lt;sup>6</sup>I may have immediately gone to MicroCenter and impulse-bought half the microcontroller aisle.

<sup>&</sup>lt;sup>7</sup> FortiProgrammer was an informal name used during early prototyping. It is not affiliated with or endorsed by Fortinet, Inc. Normally I'd worry about trademark issues, but given their usual lack of response, I felt pretty safe. The final product name **FortressFlash** is discussed in Chapter 6, Prototype to Product, as part of the branding process.

<sup>&</sup>lt;sup>8</sup>Fortinet Leadership Case Study, shared in Cyberus Entrepreneurship Course (Fall 2024).

paralleled the *FortiProgrammer* prototype's architecture, which prioritized direct serial access and physical control over configuration workflows. This perspective reinforced Fortinet's relevance—not only as the technology I had been working with extensively, but also as a model of focused, long-term design philosophy.

**Project Realignment and Scope Refinement.** The original internship, scheduled for my return to Minnesota, was supposed to revolve around developing a custom security-data dashboard for my former employer. However, a company merger soon consumed the very managers who had committed to mentor the project. With no supervisor available and key decisions—such as the choice of monitoring tools—still frozen by re-organization, the dashboard concept stalled.

Rather than wait for corporate alignment, I redirected my thesis focus to a topic that had been a recurring theme over the past two years: efficient FortiGate CLI administration. In consultation with Prof. Tegawendé Bissyandé, I presented the *FortiProgrammer* prototype—an embedded, self-contained tool for pushing standardized configurations over the FortiGate console port—as a new research focus. The faculty approved this pivot, and because I already owned the necessary hardware, I stepped-away from the organization and continued the thesis as an independent, self-directed effort.

Early drafts of the proposal had included an ambitious natural-language—to-command-line (NLP→CLI) module, but expanding the scope to full language processing would have derailed the already tight development timeline. Consequently, NLP has been reframed as future work (see Section 7.6, Intent-Based Networking): the present thesis concentrates on the practical design, implementation, and evaluation of a secure hardware—software stack, while reserving NLP-based command generation for future exploration.

#### 1.2 Problem Statement

Across the small-to-medium-enterprise (SME) sector, firewalls are rarely deployed by dedicated network engineers. Managed service providers (MSPs) must bring up dozens of client sites, each with its own topology, change window, and compliance rules. The business pressure is simple: *onboard the new box tonight; billable traffic must flow tomorrow at 08:00*. In that setting, any mis-typed CLI flag or missed firmware step is not just an inconvenience—it is downtime, SLA penalties, and reputational damage.

FortiGate appliances are popular precisely because their GUI lowers the entry barrier for routine tasks, yet the platform's most powerful features—custom SAML endpoints, FIPS-CC flash images, granular policy objects—still surface only through the command-line interface (CLI). Those commands are peculiar enough that even senior technicians keep a cheat sheet on a second monitor.

Worse, first-boot workflows occur *out-of-band* on the serial console, making them invisible to remote-management platforms that MSPs rely on for audit trails and script automation.

#### Operational pain points

- 1. Error-prone: A single syntax typo can drop VPN tunnels or expose default services.

- 2. **Inconsistent:** Step fatigue produces configuration drift, complicating long-term maintenance.

- 3. **Opaque:** Serial sessions leave no logs in remote monitoring and management (RMM) tools, hampering compliance under frameworks such as CMMC.

**Security compliance gap** – NIST 800-171 controls enforced via CMMC now require MSPs to prove that cryptographic modules (e.g., FIPS-CC firmware) load correctly, that default passwords are rotated, and that no credentials linger on removable media. A throw-away serial script on a help-desk laptop does not satisfy those controls; a signed-boot microcontroller with one-time-programmable (OTP) stored keys can.

**Research challenge**. Can a *portable*, *microcontroller-driven appliance* inject a cryptographically verified baseline configuration over the console port—*quickly*, *repeatably*, *securely*—while remaining usable by junior technicians?

### 1.3 Objectives and Scope

**Primary Objectives.** This thesis documents the design and evaluation of a self-contained, microcontroller-based tool that prepares FortiGate devices for first use over the serial console. Concretely, the work aims to:

- Design and assemble a working hardware prototype (Waveshare RP2040-Plus + ResTouch LCD + MAX3232 + microSD) capable of stable UART console I/O with FortiGate devices.<sup>9</sup>

- Implement a minimal, field-oriented firmware stack in MicroPython that provides: (i) ondevice UI for profile selection, (ii) SD-card profile discovery, (iii) a console login routine with bounded retry logic, and (iv) a serial dispatch pipeline in progress for configuration lines with prompt-aware pacing.

- Define configuration-bundle conventions (file organization, placeholders, guardrails) suitable for lab deployments and future signing.

- Produce a threat-model—driven security plan for the device (tamper, credential handling, roll-back), mapping mitigations to Pico 2 W hardware primitives for a later migration.

<sup>&</sup>lt;sup>9</sup>See Chapter 2, Hardware Design.

Secondary/Translational Objective. In addition to the technical aims, the thesis documents a strategic innovation analysis (Chapter 6, Prototype to Product). This includes a visualized Business Model Canvas, pricing hypotheses, and go-to-market framing. The purpose is to contextualize the prototype in terms of value creation for managed service providers and to reflect the program's entrepreneurship emphasis. While this analysis shaped priorities such as secure boot, credential handling, and UX polish, it does not alter the primary technical success criteria of the prototype.

Success Criteria. The prototype is considered successful for the thesis if it:

- boots to a functional UI, mounts SD, lists profiles, and exchanges CLI I/O with a FortiGate over UART in a lab setting;

- demonstrates an end-to-end configuration push *or* a verified, prompt-paced dispatch pipeline with logging ready for end-to-end trials;

- reports quantitative reliability or partial timing data when end-to-end push is not yet feasible, with the < 120 s target applied in future integration trials.

#### **Scope Delimitations.**

- **Device/OS:** FortiOS 6.x–7.x on models with RJ-45 console ports.

- **Config lifecycle:** Initial push and sanity verification only; continuous configuration management is out of scope.

- **Deferred features:** Multi-vendor support, Wi-Fi/BLE, TCP/IP API mode, and NLP/LLM intent translation are documented as *Future Work* (Chapter 7, Future Work), not deliverables for submission.

- Exploratory work captured: A Strategic Innovation track (branding, Business Model Canvas, pricing hypotheses, go-to-market framing; see Chapter 6, Prototype to Product) and limited LoRa tests (Section 7.4) are included as documented explorations that informed design but are not core technical objectives of this thesis.

### 1.4 Methodological Approach

The project followed a pragmatic, iterative process—build, test, refine—prioritizing a continuously working prototype over speculative architecture. Tasks were managed on a physical whiteboard and grouped into must/should/nice-to-have buckets. The resulting phases, along with their key activities and current status at submission, are summarized in Table 1.1.

**Phase 1** — **Requirements & Scoping.** Define the "minimum viable deployer," success metrics (e.g., < 120 s time-to-first-push), assumptions, and constraints for a field-usable tool. Capture initial risks with a STRIDE pass and explicitly delimit out-of-scope features (multi-vendor, TCP/IP API mode, NLP) for later exploration.

Phase 2 — Hardware Selection & Assembly. Select and bench-assemble the RP2040-based stack (Waveshare RP2040-Plus, MAX3232, 2.8" LCD/touch, microSD). Validate RS-232↔UART signaling to the FortiGate console, confirm stable power and cabling, and bring up display/touch and storage to ensure a reliable platform for firmware iteration.

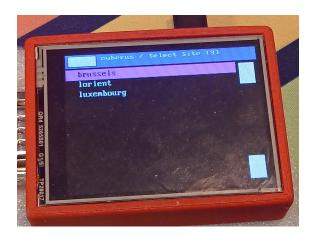

**Phase 3** — **Firmware Development.** Establish a rapid MicroPython loop (REPL + on-device execution). Implement core subsystems: stable console login with bounded retry logic, scrolling serial log, main menu touch UI, and SD profile discovery; a prompt-paced dispatch pipeline for CLI blocks remains in progress. Evolve UX from whiteboard flows to Figma frames and a linked navigation diagram; maintain small, testable commits with bench validation on a FortiGate 60E.

**Phase 4** — **Laboratory Evaluation.** Exercise subsystems on hardware to verify serial I/O, UI responsiveness, SD handling, and console login reliability; collect quantitative success rates and buffer traces; observe error cases (prompt mismatches, CR/LF quirks, buffer limits). Schedule full end-to-end timing once the dispatch path stabilizes; retain logs/screens for reproducibility.

**Phase 5** — **Security Hardening.** Deepen STRIDE analysis and define mitigations. Where timeline limits implementation, map controls to Pico 2 W primitives (signed boot, OTP-backed secrets, SHA-256, TRNG) and specify near-term measures (PIN-derived keys, bundle signing format, log redaction) as integration points for the next sprint.

**Parallel Explorations (Non-core).** Two investigations informed design but remain outside the core submission deliverables: (i) a Strategic Innovation track (branding, Business Model Canvas, pricing tiers, go-to-market framing) aligned with program outcomes, and (ii) preliminary LoRa tests to evaluate a future out-of-band control/receipt channel. These are documented to capture the full scope of inquiry without altering the technical success criteria.

Table 1.1: Project phases and current status

| Phase & Goals                          | Key Activities                          | Status                  |

|----------------------------------------|-----------------------------------------|-------------------------|

| 1. Requirements & Scoping:             | Draft objectives/scope; establish tim-  | Complete                |

| Define minimum viable deployer; set    | ing/error criteria; capture assump-     |                         |

| < 120 s metric; enumerate STRIDE       | tions/constraints                       |                         |

| threats                                |                                         |                         |

| 2. Hardware Selection & Assembly:      | Select RP2040-Plus; integrate           | Complete                |

| Stable console I/O with peripherals    | MAX3232, LCD/touch, microSD;            |                         |

|                                        | bench-verify UART                       |                         |

| 3. Firmware Development:               | Implement console login routine with    | Core subsystems         |

| Field-usable prototype UI + I/O        | retry logic; scrolling log (done); main | complete (login, log,   |

|                                        | menu UI (done); SD profile enumera-     | menu, SD); dispatch in  |

|                                        | tion (done); dispatcher for CLI blocks  | progress                |

|                                        | (in progress)                           |                         |

| 4. Laboratory Evaluation:              | Verify serial I/O, UI, SD handling;     | Console login validated |

| Validate subsystems; collect reliabil- | validate console login across 20 tri-   | (20/20); partial        |

| ity metrics                            | als; document buffer traces and error   | evaluation complete;    |

|                                        | cases; schedule end-to-end push tim-    | full push pending       |

|                                        | ing once dispatch stabilizes            |                         |

| 5. Security Hardening:                 | Plan PIN-derived keys, file-level       | Planned                 |

| Apply STRIDE; define Pico 2 W          | encryption, signed bundles, en-         |                         |

| integration points                     | crypted logs; map to Pico 2 W secure    |                         |

|                                        | boot/OTP/SHA-256                        |                         |

| -                                      | — Non-core investigations —             |                         |

| Parallel Explorations:                 | Strategic Innovation track (branding,   | Documented; not part    |

| Business/LoRa inquiries                | BMC, pricing, GTM); preliminary         | of core deliverables    |

|                                        | LoRa range/control tests for future     |                         |

|                                        | OOB channel                             |                         |

|                                        | 1                                       | 1                       |

## **Chapter 2: Hardware Design**

#### 2.1 Goals and Constraints

**FortressFlash** is a hand-held, field-deployable tool whose primary job is to push vetted baseline configurations to FortiGate appliances over the console port, reliably and repeatably, in the hands of a level-1 technician. The hardware must be simple enough to operate under time pressure in a wiring closet, yet robust and extensible enough to support future security features (e.g., signed bundles, OTP, PIN-gated access, and secure boot). This section states the goals and constraints that shaped the design; the remainder of the chapter shows how each decision traces back to these requirements.

#### Design goals.

- Deterministic serial provisioning. Establish a clean UART

RS-232 path that negotiates a console session quickly and completes a baseline push without human timing tricks.

- **Field usability.** Hand-held form factor; daylight-readable 2.8 in touchscreen; single-purpose UI with clear status and error states; operable from a USB power bank or internal LiPo battery.

- **Profile portability.** Load signed configuration bundles from microSD; support multiple customer/device profiles without reflashing firmware.

- Security readiness. Minimize attack surface (console-only path); enable PIN lock and bundle signing now; keep an upgrade path for advanced security features (signed boot, OTP, SHA-256, TRNG) without re-architecting the board.

- Extensibility. Use standard buses (SPI for LCD/touch and SD; UART for console) and modular drivers so features like audit logging, BLE/Wi-Fi convenience links, or vendor-agnostic serial templates can be added later.

- Serviceability and manufacturability. Prefer commercial off-the-shelf (COTS) modules, straightforward wiring, and a printable enclosure; document cutouts and fasteners so another engineer can reproduce the unit.

#### Key constraints.

- Cost and time. Prototype BOM and build time must remain modest to meet the thesis schedule and demonstrate repeatability (no custom PCB required).

- **Power.** Operates from standard 5 V USB sources (FortiGate, wall adapter, or portable/internal battery pack). Current draw is modest enough to run for many hours from a small power bank. Detailed electrical characterization is outside the scope of this thesis.

- **Performance headroom.** MicroPython execution and I/O throughput must keep the UI responsive while sustaining console transfers; performance measurements guide (not dictate) platform choices.

- **Physical I/O.** Honor standard DE-9<sup>1</sup> console wiring with a documented null-modem crossover; provide mechanical strain relief and basic ESD protection at the connector.

- **Reliability.** Operate without thermal hotspots or counterfeit-IC fragility; fail safely if storage is missing/corrupt or if a session is interrupted.

- **Scope limits.** No Ethernet, TCP/IP, or cloud control in this chapter; those appear in Future Work and require additional networking and API surfaces.

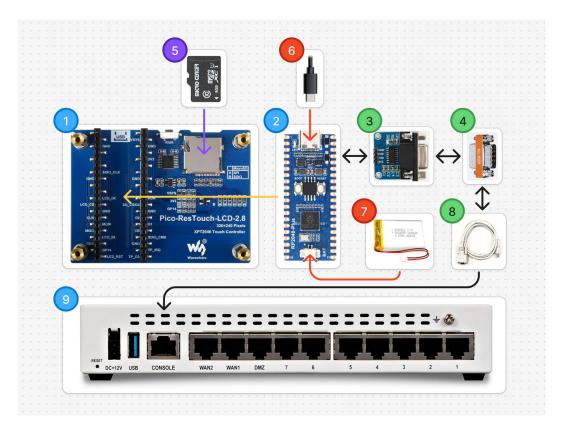

**System overview.** At a high level (see block diagram in Figure 2.1), USB-C power and an optional LiPo battery (6,7) supply the RP2040-Plus MCU module (2). The MCU drives an SPI<sup>2</sup> bus to the Waveshare Pico-ResTouch carrier (1), which integrates the 2.8 in LCD, XPT2046 touch controller, and the removable microSD socket; the microSD card (5) holds configuration bundles and profile data. The MCU also exposes a UART that interfaces to a MAX3232 RS-232 transceiver breakout (3), which provides a DE-9 connection; a male–male null-modem adapter (4) and the standard DE-9 console cable (8) implement the required crossover wiring to the FortiGate console port (9). This partition keeps the ±RS-232 domain electrically isolated from the MCU's 3.3 V logic and makes each subsystem independently verifiable.

The following sections walk through the numbered subsystems: the MCU (2) in Section 2.2; display and storage (1,5) in Section 2.3 (Waveshare ResTouch 2.8" — overview); power (6,7) in Section 2.3 (Power and battery); the serial interface and cabling (3,4,8,9) in Section 2.4; and enclosure and assembly notes in Section 2.5.

<sup>&</sup>lt;sup>1</sup>Formally the nine-pin D-sub shell size is DE-9; "DB-9" is a widely used colloquialism inherited from the common DB-25 connector label.

<sup>&</sup>lt;sup>2</sup>SPI (Serial Peripheral Interface) is a synchronous serial bus used for short-distance, high-speed connections between a master (MCU) and one or more slaves (displays, SD cards, sensors). Typical lines: SCLK, MOSI, MISO, CS.

Figure 2.1: FortressFlash hardware block diagram, showing major subsystems: (1) 2.8 in LCD + touch controller + microSD carrier (Waveshare Pico-ResTouch), (2) RP2040-Plus MCU module, (3) MAX3232 RS-232↔TTY breakout, (4) DE-9 male ← male null-modem adapter, (5) microSD card for configuration bundles, (6) USB-C port for power and programming, (7) optional LiPo battery, (8) standard DE-9 console cable, and (9) FortiGate firewall console port. Data flows from the MCU to the FortiGate console via UART→RS-232 conversion, while SPI buses connect the LCD, touch controller, and SD storage. Power can be provided by USB-C or battery.

#### 2.2 Candidate MCU Platforms and Selection

Several development platforms (see Figure 1.3) were evaluated for suitability with the FortressFlash prototype, including the TinkerKit LCD, Arduino Mega, the Raspberry Pi Zero 2 W, the Raspberry Pi Pico (RP2040 family), and the RP2040-Plus module that was chosen for the prototype (Table 2.1). The core selection criteria emphasized reliable UART and SPI I/O, a compact handheld form factor, and a modest BOM cost to enable rapid, reproducible prototyping. During the hands-on evaluation phase, the RP2040's MicroPython ecosystem proved invaluable for rapid firmware development, and the later appearance of the Pico 2 W indicated a plausible upgrade path to hardware security primitives—both benefits that reinforced the RP2040-based choice. The block diagram in Figure 2.1 shows the final architecture; the remainder of this section explains why the RP2040-Plus best balanced the stated constraints and how that choice shaped downstream subsystem design.

TinkerKit LCD (Arduino Leonardo). Early testing was performed using the TinkerKit LCD module, which includes a built-in 16×2 LCD and servo headers for quick GPIO prototyping [4]. This legacy board, based on the Arduino Leonardo, was convenient to experiment with because several units were available from prior stock—despite it being discontinued and no longer supported by TinkerKit [5]. However, its single UART interface quickly proved insufficient: the board could not simultaneously communicate with the FortiGate and also initiate a connection to the Arduino IDE for debugging. This prompted investigation of another board already on-hand, the Arduino Mega.

**Arduino Mega.** A slight upgrade to the Arduino Mega ADK R3, with its four hardware UARTs, immediately solved the serial-interface limitation [6]. Its larger I/O footprint also made it easy to integrate additional peripherals. However, the Mega lacks a built-in display and, as a design, also represents a legacy-class board—large and relatively expensive for its capabilities compared to newer options. More broadly, both the Mega and other Arduino boards such as the TinkerKit LCD share the platform's underlying 8-bit AVR architecture and limited flash storage, which impose tight constraints on program size and have become increasingly outpaced by modern microcontrollers.

Raspberry Pi Zero 2 W. Attention then turned to the much more robust Raspberry Pi boards; and the next to be evaluated was the Zero 2 W, which proved to be an excellent platform—more than capable of meeting all the project's requirements with its quad-core CPU, 512 MB of RAM, and microSD storage [9]. However, the fact that it is a full Linux system meant that it was, in a sense, *too capable*, introducing additional considerations such as OS selection, updates, and patches that would complicate the build. In a context where simplicity and deterministic behavior were priorities, this level of complexity would have introduced unnecessary maintenance overhead and potential points of failure over time.

Raspberry Pi Pico W. Ruling out the Zero 2 W left the Pico W as the next candidate. Although this board includes on-board Wi-Fi/BLE, wireless functions were not used in this project; evaluation focused on the RP2040 platform itself. The Pico W offered an effective balance of capability and simplicity: its dual-core Arm Cortex-M0+ at 133 MHz and ample SRAM provided far more headroom than 8-bit Arduino-class boards while retaining a deterministic, bare-metal feel without the overhead of a full Linux system [7]. Its low cost, small footprint, and mature MicroPython/toolchain ecosystem made it a solid base for the prototype, with broad community adoption indicating good long-term ecosystem support.

Table 2.1: Comparison of candidate boards by specification. See notes for feature-specific remarks. Technical specifications derived from official datasheets and product briefs [4, 5, 6, 7, 8, 9].

| Spec                     | TinkerKit LCD                        | Arduino Mega                          | Raspberry Pi                          | Raspberry Pi                          |

|--------------------------|--------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

|                          | (Leonardo) <sup>a</sup>              | 2560                                  | Pico (Pico 2) W                       | Zero 2 W                              |

| CPU                      | ATmega32u4 @                         | ATmega2560 @                          | Dual ARM M0+                          | Quad ARM-A53                          |

|                          | 16 MHz                               | 16 MHz                                | @ 133 MHz (M33                        | @ 1 GHz                               |

|                          |                                      |                                       | @ 150 MHz) <sup>b</sup>               |                                       |

| RAM                      | 2.5 KB SRAM                          | 8 KB SRAM                             | 264 KB (520 KB)                       | 512 MB RAM                            |

|                          |                                      |                                       | SRAM                                  |                                       |

| Flash                    | 32 KB onboard                        | 256 KB onboard                        | 2 MB (4 MB)                           | No onboard Flash                      |

|                          |                                      |                                       | onboard                               |                                       |

| Security                 | None (no hard-                       | None (no hard-                        | None (Pico); Pico                     | OS-level only; no                     |

|                          | ware security)                       | ware security)                        | 2: Signed boot,                       | dedicated MCU                         |

|                          |                                      |                                       | OTP key storage,                      | security features                     |

|                          |                                      |                                       | SHA-256, TRNG <sup>c</sup>            |                                       |

| Interfaces               | $1 \times \text{UART}, I^2\text{C},$ | $4 \times \text{UARTs}, I^2\text{C},$ | $2 \times \text{UARTs}, I^2\text{C},$ | $2 \times \text{UARTs}, I^2\text{C},$ |

|                          | SPI                                  | SPI                                   | SPI, PIO                              | SPI, USB                              |

| Expansion                | None                                 | None                                  | External SD via                       | microSD slot for                      |

|                          |                                      |                                       | add-on                                | OS and storage                        |

| WiFi / BT                | No / No                              | No / No                               | Yes (802.11n) /                       | Yes (802.11n) /                       |

|                          |                                      |                                       | Yes (BT 5.2) <sup>d</sup>             | Yes (BT 4.2)                          |

| Logic Voltage (V)        | 5                                    | 5                                     | 3.3                                   | 3.3                                   |

| Draw (mA) <sup>e</sup>   | ~50 typical                          | ~70 typical                           | ~90 typical +                         | ~100–160 idle,                        |

|                          |                                      |                                       | peripherals                           | higher under load                     |

| Board Size (mm)          | 68 × 53                              | 101 × 53                              | 51 × 21                               | 65 × 30                               |

| Languages                | C / C++ (Arduino                     | C / C++ (Arduino                      | C / C++ (SDK),                        | Full Linux stack                      |

|                          | IDE)                                 | IDE)                                  | MicroPython,                          | (Python, C/C++,                       |

|                          |                                      |                                       | CircuitPython                         | Node.js, etc.)                        |

| Price (USD) <sup>f</sup> | ~ \$20                               | ~ \$25                                | ~ \$6 (\$7)                           | ~ \$15                                |

<sup>&</sup>lt;sup>a</sup> The TinkerKit LCD was actively sold prior to 2015 and is now discontinued.

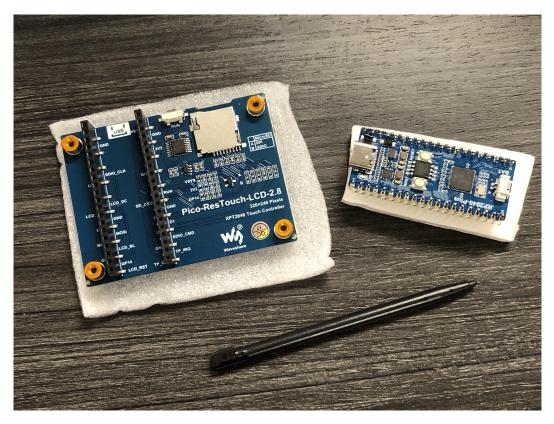

Waveshare RP2040-Plus. While the Raspberry Pi Pico platform was selected for its balance of simplicity and capability, a third-party variant—the Waveshare RP2040-Plus—was ultimately chosen for the prototype due to several practical enhancements. It retains the RP2040 MCU but expands on-board flash to 16 MB (versus 2 MB on a standard Pico), providing ample space for firmware, fonts, and user data. It also integrates Li-ion charge/discharge for untethered field operation. Notably, it has *no on-board radio*. These upgrades, combined with drop-in compatibility with Pico headers and peripherals, made it a strong foundation for this build (Figure 2.3).

**Upgrade Path (Pico 2 W).** Mid-project, Raspberry Pi introduced the Pico 2 W (RP2350), which adds a faster core (150 MHz), expanded RAM (520 KB) and on-chip flash (4 MB), plus security features absent on Pico 1. Because it is pin-compatible, migrating is trivial (reflash the UF2 and

<sup>&</sup>lt;sup>b</sup> Pico 2 uses the RP2350 chip, featuring dual Cortex-M33 or selectable Hazard3 RISC-V cores.

<sup>&</sup>lt;sup>c</sup> Pico 2 introduces enhanced security including signed boot support, 8 KB OTP storage, hardware SHA-256 accelerator, and a hardware true random number generator.

<sup>&</sup>lt;sup>d</sup> Wi-Fi (802.11n) and Bluetooth 5.2 are available only on the Pico W and Pico 2 W models.

<sup>&</sup>lt;sup>e</sup> Power consumption values are approximate typical current draw measured at 5 V input (USB or 5 V pin), even for boards with 3.3 V logic internally.

f Prices shown are launch MSRPs; current availability and market prices may differ.

reboot). Although time constraints prevented a full migration for this thesis, the Pico 2 W's security primitives—signed boot, hardware-backed OTP key storage, on-chip SHA-256, and a TRNG—directly support planned milestones such as a verifiable secure-boot chain, sealed credential vaults, and integrity-checked configuration bundles. Adopting the Pico 2 W in future iterations would therefore boost performance and provide a hardware-rooted trust anchor that aligns with embedded-security best practices.

Alternate Upgrade Path (ESP32-S3). While the Pico 2 W is a drop-in upgrade, the ESP32-S3 is a credible alternative when integrated radios and memory options are desired. It offers dual-core Xtensa, 2.4 GHz Wi-Fi + BLE, plentiful I/O, and mature MicroPython support, plus SoC-level secure-boot and flash-encryption in the ESP-IDF toolchain. A representative board-level reference is Heltec's WiFi LoRa 32 V3 (ESP32-S3), which couples Wi-Fi/BLE with LoRa and common QSPI flash/PSRAM configurations [10]. Practically, for this project's UART-driven, UI-light workflow, the Pico family's determinism and the RP2350's hardware security features make it the default; the S3 is best kept for radio-heavy or OTA-first variants, e.g., future additions as discussed in Section 7.4, Long-Range Wireless: LoRa.

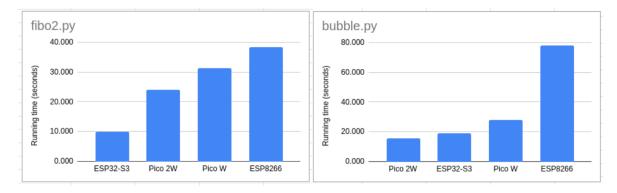

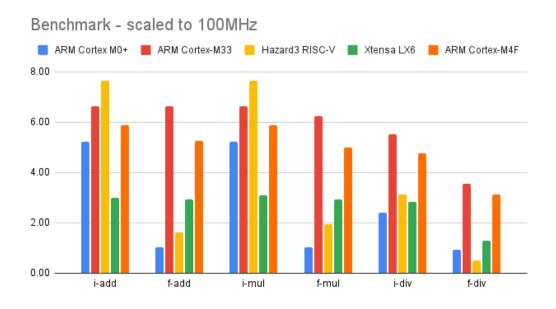

**Benchmark snapshot** (MCU-only). To keep comparisons apples-to-apples, this snapshot covers *MCU-class* boards only (RP2040/Pico, RP2350/Pico 2, ESP32 family); *Arduino-class 8-bit* and *Linux-class* boards (e.g., Raspberry Pi Zero 2 W) are excluded. Table 2.2 summarizes representative MicroPython results that primarily compare Pico 1 (RP2040) and Pico 2 (RP2350); any ESP32 rows in the table refer to earlier ESP32 (LX6) devices and are provided for context—not the ESP32-S3. For a direct Pico W vs. Pico 2 W vs. ESP32-S3 view, the time-based benchmarks reproduced in Figure 2.2 show workload-dependent rankings: bubble.py favors Pico 2 W over ESP32-S3 and Pico W, while fibo2.py favors ESP32-S3 over Pico 2 W and Pico W [11]. Additional arithmetic MOPS charts for RP2040↔RP2350 appear in Appendix Figures A.5–A.6, which support the Pico 2 headroom claims without implying a universal ordering across all workloads [12, 13].

Table 2.2: MicroPython Benchmark Results Across Selected Platforms

| Board                         | CPU      | MHz | PS/s <sup>a</sup> | i-add | f-add | i-mul | f-mul | i-div | f-div |

|-------------------------------|----------|-----|-------------------|-------|-------|-------|-------|-------|-------|

| PC                            | Intel    | _   | 200               | _     | _     | _     | _     | _     | _     |

| Pico                          | RP2040   | 133 | 1.08              | 6.95  | 1.36  | 6.94  | 1.38  | 3.22  | 1.23  |

| Pico 2 (M33)                  | RP2350   | 150 | 2.48              | 9.96  | 9.97  | 9.97  | 9.34  | 8.30  | 5.34  |

| Pico 2 (Hazard3) <sup>b</sup> | RP2350   | 150 | 2.48              | 11.49 | 2.41  | 11.49 | 2.93  | 4.67  | 0.74  |

| Wemos                         | ESP32    | _   | 1.04              | _     | _     | _     | _     | _     | _     |

| M5Stack Core                  | ESP32    | 240 | 0.66              | 7.23  | 7.02  | 7.45  | 7.02  | 6.81  | 3.14  |

| Wio Terminal                  | ATSAMD51 | 120 | _                 | 7.05  | 6.31  | 7.04  | 5.99  | 5.70  | 3.74  |

<sup>&</sup>lt;sup>a</sup> PS/s = Pystones per second.

Sources: Data compiled from Ardusimple [12] (Pystones) and Cheppali [13] (MOPS benchmarks).

<sup>&</sup>lt;sup>b</sup> Pico 2 Hazard3 scores are for the secondary RISC-V core on the RP2350.

Figure 2.2: Time-based MicroPython benchmarks on MCU-class boards (Pico W, Pico 2 W, ESP32-S3): left, fibo2.py; right, bubble.py. Reproduced from Grinberg [11]. Rankings vary by script; see text for discussion.

### 2.3 Subsystems: Display, Touchscreen, Storage, and Power

Waveshare ResTouch 2.8" — overview. The prototype uses the Waveshare Pico-ResTouch 2.8" carrier as the integrated display, touch, and removable-storage subsystem. This carrier plugs directly onto the Pico-style header of the RP2040-Plus module, minimizing wiring and simplifying assembly. The reader can find the prototype's GPIO and peripheral-bus assignments for the carrier in Table 2.3.

**LCD** (display). The ResTouch provides a 2.8-inch IPS panel with a 320×240 QVGA pixel matrix that is sufficient for rendering FortiGate CLI text and simple status screens [14]. In practice the display is driven over an SPI bus from the MCU and uses a modest framebuffer strategy to keep redraw latency low while preserving MicroPython responsiveness; implementation details and driver notes are discussed in Section 3.5. The display hardware and required SPI signals are summarized in Table 2.3.

**Touch (XPT2046).** Touch input is provided by an XPT2046 resistive touch controller on the carrier. The touch controller communicates via SPI (MISO is read by the XPT2046 only) and raises an IRQ line when contact is detected; a lightweight calibration routine maps raw ADC touch coordinates into screen pixels. The firmware implements debouncing and a simple two-point calibration workflow to keep touch calibration fast and robust for field technicians. Relevant pin assignments and the active IRQ polarity are listed in Table 2.3.

**Removable storage (micro-SD).** Configuration bundles and user profiles are stored on the carrier's removable micro-SD socket; the prototype uses FAT32 for interchangeability across platforms. Firmware remains on the RP2040-Plus module's onboard flash (separate from the SD card), while the SD card holds text-based CLI bundles that the device loads at run time. The card is mounted at

Figure 2.3: Waveshare RP2040-Plus microcontroller (right) and Pico-ResTouch-LCD-2.8 touchscreen module (left), showing the dual-row header that mates the two boards, the onboard micro-SD socket, and the resistive stylus used for input.

/sd; the current firmware presents a clear "no card" error state when a card is absent. SD handling code can be extended to verify bundle integrity (for example by checking a checksum or signature) and to detect corrupt or partially written files. Typical CLI bundles are modest in size (tens to a few hundred kilobytes), so SD transfer latency is unlikely to be a user-visible problem for configuration pushes. Migration to a Pico 2 W would preserve this storage layout while enabling optional signing and encryption of bundles as discussed in Chapter 4, Threat Modeling.

**Power and battery.** FortressFlash is designed to run from universal 5 V USB sources (for example a USB-C power bank, a wall adapter, or even the USB port on a FortiGate appliance or laptop) and may also be fitted with an optional LiPo cell for untethered use. The RP2040 core and peripherals operate at 3.3 V; the RP2040-Plus MCU module used in the prototype includes an on-board switch-mode regulator rated well above the device's steady-state draw (the regulator is specified to supply up to 2 A at 3.3 V) [15].

In practice the Waveshare ResTouch + Pico stack runs comfortably from common USB supplies—Waveshare documentation and hands-on testing with a vanilla Pico suggest the combined draw is on the order of a few hundred milliamps under normal UI and console-transfer activity [14]. Future hardware expansions—such as LoRa, Wi-Fi, or higher-brightness backlights—could exceed this

Table 2.3: Prototype GPIO and Peripheral-Bus Assignments

| RP2040-Plus Pin(s)                                                        | Signal (bus)                                       | Connected Peripheral / Purpose              |  |  |  |  |

|---------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------|--|--|--|--|

| Serial console to FortiGate (via MAX3232 level shifter)                   |                                                    |                                             |  |  |  |  |

| GP0 UART0_TX TXD → RS-232 pin 2 (Null-modem crossover to FortiGate Rx     |                                                    |                                             |  |  |  |  |

| GP1                                                                       | UART0_RX                                           | RXD ← RS-232 pin 3 (from FortiGate TxD)     |  |  |  |  |

| <b>3V3</b> (pin 36)                                                       | VCC                                                | Powers MAX3232 board (3 V logic side)       |  |  |  |  |

| <b>GND</b> (pin 28)                                                       | Ground                                             | Common return for MAX3232 and display stack |  |  |  |  |

|                                                                           | ResTou                                             | ch 2.8 in. LCD (ST7789) — SPI 1 bus         |  |  |  |  |

| GP10                                                                      | SPI1 SCK                                           | LCD CLK                                     |  |  |  |  |

| GP11                                                                      | SPI1 TX                                            | LCD MOSI                                    |  |  |  |  |

| GP12                                                                      | SPI1 RX                                            | LCD MISO (only used by touch/XPT2046)       |  |  |  |  |

| GP8                                                                       | LCD_DC                                             | LCD Command/Data pin                        |  |  |  |  |

| GP9                                                                       | LCD_CS                                             | LCD chip-select                             |  |  |  |  |

| GP15                                                                      | GP15 LCD_RST LCD hardware reset                    |                                             |  |  |  |  |

| GP13 LCD_BL PWM back-light drive                                          |                                                    |                                             |  |  |  |  |

|                                                                           | XPT2                                               | 2046 Touch-controller (shares SPI 1)        |  |  |  |  |

| GP16                                                                      | TP_CS                                              | Touch-controller chip-select                |  |  |  |  |

| GP17                                                                      | TP_IRQ                                             | Touch IRQ (active-low pen-down)             |  |  |  |  |

|                                                                           | On-boa                                             | rd micro-SD slot (4-bit SDIO interface)     |  |  |  |  |

| GP5                                                                       | SDIO_CLK                                           | SD clock                                    |  |  |  |  |

| GP18                                                                      | SDIO_CMD                                           | SD command (DI)                             |  |  |  |  |

| GP19                                                                      | SDIO D0                                            | Data bit 0 (also SPI MISO fallback)         |  |  |  |  |

| GP20                                                                      | SDIO D1                                            | Data bit 1                                  |  |  |  |  |

| GP21                                                                      | SDIO D2                                            | Data bit 2                                  |  |  |  |  |

| GP22                                                                      | GP22 SD_CS/D3 Data bit 3 / chip-select in SPI-mode |                                             |  |  |  |  |

|                                                                           | Miscellaneous / power                              |                                             |  |  |  |  |

| VSYS (pin 39) 5 V input Powers ResTouch via header (USB-C or Li-ion pack) |                                                    |                                             |  |  |  |  |

#### Notes:

- For annotated pin-out diagrams of the Waveshare RP2040-Plus and the ResTouch 2.8 in. LCD, see Appendix A.2, Pinout Diagrams.

- The ResTouch header hard-wires every line shown; no additional jumper wires are required once the RP2040-Plus is inserted.

- SPI1 is used for both the ST7789 LCD and the XPT2046 touch-controller; chip-selects keep the buses independent.

- The MAX3232 board's DE-9 connector follows a DCE pin-out and mates to the FortiGate rollover cable through a male—male null-modem adapter, as illustrated in Fig. 2.4.

envelope when powered from a standard Pico or Pico 2. In such cases a dedicated 5 V rail or an external regulator may be necessary to maintain stability under peak loads. For field use a modestly rated USB supply (1 A or higher at 5 V) provides useful headroom; many modern phone chargers and power banks provide 2 A or more.

## 2.4 Subsystems: Serial UART

As with most professional-grade networking gear, FortiGate appliances expose a serial console for direct access to the command-line interface (CLI). On earlier mid-range models—such as the **60D**—the console appears on a mini-USB USB MGMT port that contains an on-board serial-to-USB bridge. Fortinet dropped that feature in later revisions. The **60E** unit used throughout this project instead

presents the console on an RJ-45 (Cat 5) jack; Fortinet ships it with an RJ-45-to-DE-9 (female) rollover cable for connection to a standard RS-232 port. The console ports are visible on the rear panels of the three stacked firewalls in Figure 1.1 and the block diagram in Figure 2.1, labeled CONSOLE and located to the right of the DC jack.

While initial testing was performed using a USB-to-RJ-45 console cable (occasionally included with newer FortiGate units), a standard USB-to-DE9 (male) serial adapter was used when a direct RS-232 connection from a workstation was required. This arrangement allowed for quick changeovers between the development workstation and the prototype without needing to swap console cables, since both relied on the same DE-9 connector and rollover cable. What follows is a breakdown of how the serial interface was integrated into the prototype hardware, along with issues that emerged during testing and iteration.

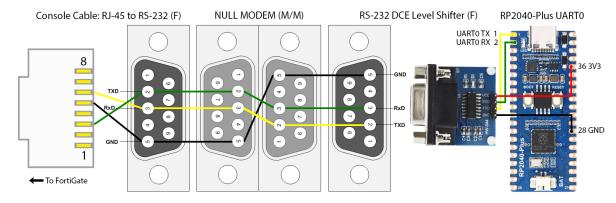

Pinout Mapping and Cable Configuration Figure 2.4 illustrates the complete console wiring path used for the prototype. The FortiGate's RJ-45 console port connects to a Fortinet rollover cable terminating in a DE-9 (female) DCE connector. This connects through a DE-9 male-to-male null-modem adapter, which crosses the transmit and receive lines. The other end of the null-modem feeds into a MAX3232-based RS-232 level shifter, which presents another DE-9 (female) DCE interface. The level shifter converts standard RS-232 voltage levels to 3.3 V TTL, which are connected to UARTO on the RP2040-Plus. In addition to the signal lines, the RP2040-Plus provides a regulated 3.3 V output and ground connection to power the HX-004 level shifter directly. This chain enables seamless communication between the FortiGate console and the microcontroller while maintaining signal integrity and logic-level compatibility.

Figure 2.4: Signal flow from FortiGate RJ-45 console port to UART0 on the RP2040-Plus MCU, via standard RS-232 and HX-004 level-shifting components. Adapted from sources [16, 17, 15].

#### **MAX3232 Converter Thermal Faults**

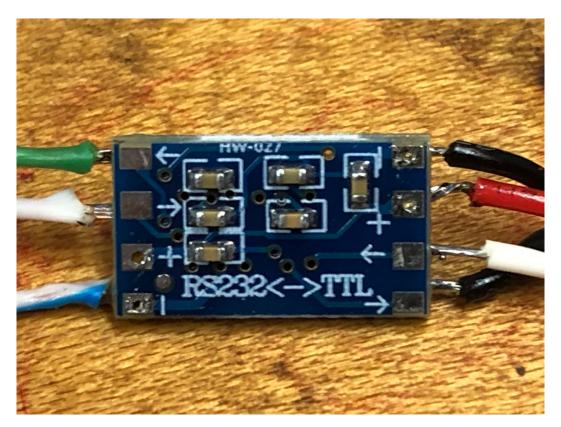

**Symptom.** Early designs used a postage-stamp HW-027 "RS-232 $\leftrightarrow$ TTL" board (15 mm  $\times$  9 mm) to level-shift the FortiGate console. Even with  $V_{CC}$  (3.3 V) and GND correctly wired on the logic edge *and* no load on the RS-232 side, the board overheated within seconds. This behavior contrasted sharply with the low standby current ( $\sim$ 1 mA) specified in the official TI MAX3232 datasheet [18], indicating the presence of a faulty or counterfeit chip (see Figure 2.5).

#### **Root–cause analysis.** Two factors remained:

- a) **Mirrored silkscreen.** The board prints "VCC" on both long edges; the RS-232 edge is actually the  $V_+$  charge-pump node ( $V_{CC} + 6$  V). Powering this pad latches the chip in a high-current state.

- b) **Counterfeit silicon.** Many low-cost breakouts ship with look-alike chips that omit the tiny internal bias resistors. With those resistors missing, unused inputs float, the device switches itself rapidly, and the package overheats—regardless of perfect pinout [19, 20].

**Attempted community fix.** An Amazon reviewer (*ET*) published a "corrected" pinout after tracing the IC leads with a multimeter [21]. Replicating that wiring eliminated the obvious latch-up mistake, yet the module still idled hot—evidence that the problem was deeper than silkscreen confusion.

**Resolution.** The prototype now uses a larger HX-004 breakout (see Figure 2.4). Although it still carries a low-cost, non-TI MAX3232 clone, the board includes all five 100 nF charge-pump capacitors and a tidier layout, so it idles cool. Its right-angle DE-9 *female* connector is wired for the standard *data-terminal-equipment* (DTE) pinout (pin 2 = RxD, pin 3 = TxD). The FortiGate console cable behaves as *data-communication-equipment* (DCE) (pin 2 = TxD, pin 3 = RxD). To create the required crossover and match connector genders, a 6 cm *male-to-male* null-modem adapter that swaps pins  $2 \leftrightarrow 3$  is inserted in-line.

**Future-proof option.** Should the design be miniaturised again, a quality-controlled module such as the *Adafruit RS-232 Pal* (Product 5987, \$3.95) provides a TI-branded MAX3232E and clear silkscreen, eliminating clone-silicon risk entirely [22].

#### Lessons learned.

• Source traceable components. The \$1 clone modules consumed more engineering time than a \$4 proven breakout.

Figure 2.5: Close-up of the HW-027 RS-232↔TTL level-shifter board implicated in early thermal issues.

• **Document hidden pin conventions.** A single BoM note about the mirrored silkscreen and DTE pinout would have halved debug time.

### 2.5 Enclosure and Connector Integration

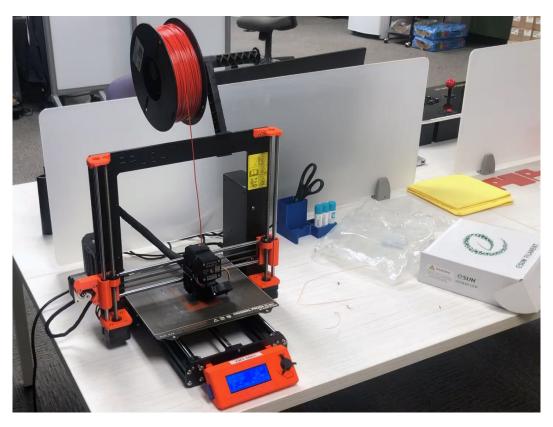

The prototype is housed in a 3D-printed enclosure based on a design published on Thingiverse by Tasuku Suzuki [23]. The model, originally intended for the Waveshare 2.8" capacitive touchscreen and Raspberry Pi Pico, was selected due to its close alignment with the chosen hardware stack and its availability under a permissive CC BY-SA license.<sup>3</sup> The enclosure was printed in-house using red ABS filament from eSUN on a Prusa i3 MK3S+, with only minor fit adjustments, as shown in Figure 2.6.<sup>4</sup>

During early design planning, an RJ45 keystone jack was considered for the RS-232 interface, allowing the use of standard CAT5 cables for console connections. This would have provided a clean, low-profile rear connector. As discussed in Section 2.4, MAX3232 Converter Thermal Faults, however, the unbranded MAX3232 module used in this configuration exhibited unsafe thermal behavior and was ultimately rejected.

<sup>&</sup>lt;sup>3</sup>For a render of the original enclosure model, see Figure A.3 in the appendix.

<sup>&</sup>lt;sup>4</sup>For a view of the enclosure mid-print on the Prusa i3 MK3S+, see Figure A.4 in the appendix.

Figure 2.6: Waveshare 2.8" LCD and RP2040-Plus mounted in 3d-printed ABS case.

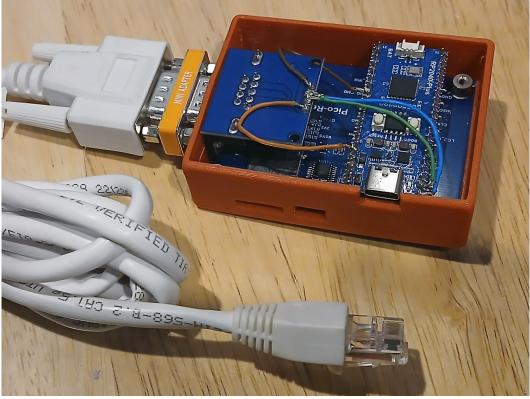

A more robust MAX3232 breakout board with a built-in DE-9 female connector was adopted to serve as the stable, long-term solution for the console interface. As the enclosure did not feature a cutout for either connector type, the DE-9 port was temporarily hand-fit during prototyping to create a side opening. While this modification enabled functional access to the serial port, it prevented the rear panel from being re-attached. Due to time constraints, a proper CAD remix of the original STL file was deferred, but future revisions will likely address this with a clean rear-mounted DE-9 cutout or a revised modular panel system. Despite this compromise, the prototype remains fully operational, and the enclosure provides sufficient structural protection and screen stability for lab testing and demonstration purposes.

## 2.6 Complete FortressFlash Assembly

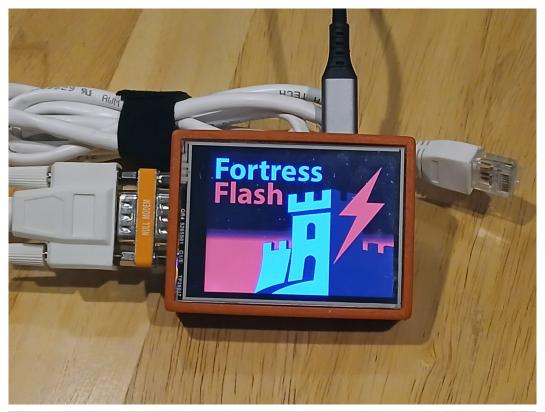

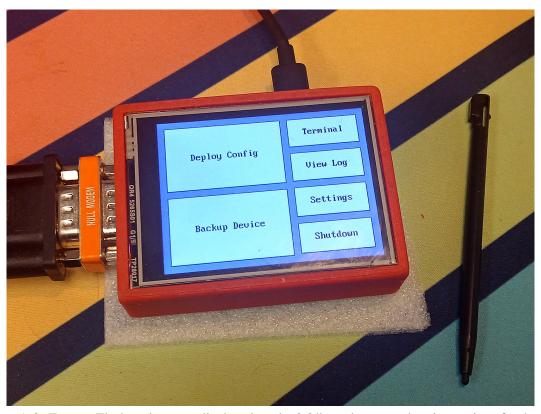

With all major subsystems integrated—MCU, display, storage, UART interface, and enclosure—the prototype reaches its final field-ready form. The completed device unites these elements into a single hand-held tool, compact enough for deployment by entry-level technicians while robust enough to support future enhancements. Figure 2.7 shows the complete FortressFlash assembly from both front and rear perspectives.

Figure 2.7: Complete FortressFlash assembly. Front view powered on with splash screen and attached DE-9 console cable via in-line null-modem adapter (top), and rear view exposing the RP2040-Plus module, wiring, and DE-9 connector integration (bottom).

## **Chapter 3: Software Design**

### 3.1 MicroPython for Rapid Prototyping

When evaluating firmware options for the device, MicroPython emerged as the most practical choice for rapid prototyping. Unlike traditional C/C++ development with the vendor SDK—which requires a full toolchain setup, compilation cycles, and more rigid debugging—MicroPython provides an interactive, high-level environment directly on the microcontroller. Its REPL (Read–Eval–Print Loop) enables immediate feedback from the hardware, allowing code to be tested, modified, and re-deployed in seconds. This dramatically shortens the iteration cycle compared to a compile–flash–reset workflow, and its Pythonic syntax minimizes repetitive setup code, making it easier to express hardware interactions such as GPIO, UART, SPI, and I<sup>2</sup>C in clear, concise statements.